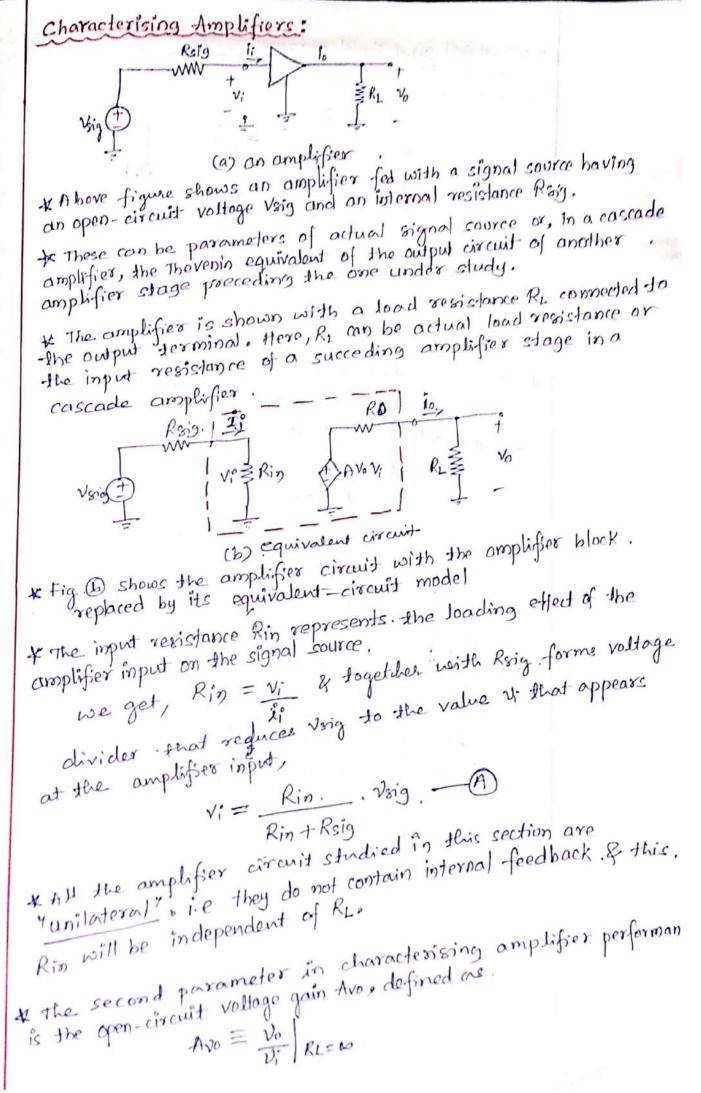

Module - 2 Toransistood Biasing Totansistoor bias - The porocess of setting the operating Point of a totansistor for its stable g oreliable performance. Different times of here Prototype - Basic circuit design -> Base bias - used in design of switching circuits -> Emitten " - " " " " amplifying " Different types of bias -> Emitten " Voltage Divideor Bias (self Bias on Base Bios) The bias circuit that contains voltage divider (Rigra) at the base is called voltage - divideor bias (VDB). 9 +Vcc +Vcc o trac 3Rc N RIZIA ZRc/Ic ABAN RI +VBB => IB VBB VE SRE RETE RE Fig2. VDB Cioncuit. Fig2: Voltage divideor Fig.35 implified VDB Cioncuit. Cioncuit -> Fig. I shows voltage divider bias cincuit. -> Rigre divides the voltage at the base. -> Base cuarrent IB is very small gave -> We can open the torunsistor mentally & equivalent A voltage divideor cioncuits looks like as in fig2 > Base supply voltage VBB is given by  $VBB = \frac{R_2}{VCC}$ R1+R2

3:1 By applying KVL at the loop in fig. 3 (Base-emily 7.6 VBB - VBE - VE. = O VE = VBB-VBE VE = IE RE IE = VE IB is very small  $I_{E} = I_{C} + I_{B}$ IC YIE VC = VCC - ICRC Collector to Emother voltage VCE = NC - VE Analysis steps for VDB (6 steps) 1. Calculate NBB for VDB. Find VE = VBB - VBE Where VBE=0.7 2. TE = VE RE З, 4. Assume IC SIE Calculate the collector -to-ground voltage (Ve) by substanctin voltage across the collector CTCR 5. presistor forom collector supply (vcc) a 6. Calculate VCE = VC - VE. S. R. & B. Winnes In Accustate VDB analysis It is the one in which the voltage divider appears stiff to the input resistance of the base ~>

Stiff voltage source Rs < 0.01 RL 3 > Rs must be loo times RL. -> we have VDB cioncuit as, , tycc FillR2 FRC RIS Rc -O < RTH RIN R2 Z VBB-ERE RE Thevenin oursistance. Equivalent cioncuit Input oresistance > Therenin resistance RTH = RILLR2 if act as Sounce resiston Re -> voltage divideor sees a load oresistance of RIN So RIN here is nothing but RIN -> Voltage divider to appear stiff to the base it has to follow 100:1 rule. RS < 0.01 RL. RS = RTH = RILLR2 RillR2 20.01 RIN RL = RIN Well designed VDB circuit will satisfy this condition. stiff voltage divider. -> If Toransistor has a cuorment gain (Bolc) of 100 Ic = (Bdc) 100 IB, IE = (Bdc) 100 IB. Forom the base RE appears to be loo times laorgeon . RIN = Bolc RE Stiff voltage: RillR2 < 0.01 Bdc RE divideor

> Whenever possible, a designer selects circuit Values to satisfy this 100:1 stule. It will Poroduce an ultorastable g-point -> Some times a stiff design gresults in such a small values of R1. 8 R2 that other problem arises ->. Many designeous componentise by using this oute. Fioron voltage dividen: RillR2 < 0.1 Bdc RE. -> voltage divideor that satisfies 10:2 oute called as firm voltage divider. ~ VDB circuit has a reasonably stable g point. -> If we want a more accurate value of emitter current. ITE = NBB- VBE and the spectrum of the spectru -> above equation will imporove the anerlysis but it is a complicated footoonula. QUI & EHTA - AL - AL VDB and Load Line and g point -> As we have stiff voltage dividen cincuit, to analyze load line & g point. VE is held constant i,e  $V_E = 1.1 v.$ P. P. William > If we have NCE = 4.94V & Ic = 1.2 mA > If we plot it on the graph will get the g point as following. and aller

Vel lotes " in the station of the

and the ba

Ri blez RC

Ri blez RC

3.6k.2 Tread GH

RE

2.2k.2 RO

Calculating the g point

(acoust of the g point of coll not

change divideat bias is the modification of

emitter bias. CRd)

> If ausient gain changes g point of coll not

change (move).

One way to move the g point is by varying

the emitter gesistor RE.

Condition -2. If RE changed to 2.2 kD2 TC onTE

decoreases. to.

TE= alt\_2.9 V = 0.5mA, Consider. VE = 2.2 V

RE 2.2 KD

The voltage VC changes

VC = tov VCC - IC RC

$$= 10 - (0.5mA) (2.6 KD)$$

$[VC = 8.2V]$ .

S VCE = VC - VE

$= 8.2 - 1.1$ .

$[VCE = 7.1V]$

> G shifts de now g is called gL with Co-ordinates

(0.5mA, 7.1 V)

(VCE TC)

Condition -2 If RE decoreased to S10 JZ , TE

on TC - increases to:

$$T_{E} \subseteq T_{C}, \qquad T_{E} \equiv T_{C} + T_{E} \text{ is small}$$

$$I_{E} = \underline{9}, \underline{9} = 2.15 \text{ mA}$$

$$\overline{I_{C}} = \underline{2.15 \text{ mA}}$$

$$\overline{I_{C}} = \underline{2.15 \text{ mA}}$$

$$V_{C} = M_{C} - I_{C} R_{C}$$

$$\equiv 10 - 2.15 \text{ mA} 3.6 \text{ kJ2}, \qquad V_{C} = 2.26 \text{ V}, \qquad \text{and}$$

$$V_{C} E = V_{C} - V_{E}$$

$$= 2.26 \text{ V}, \qquad \text{and}$$

$$V_{C} E = 1.16 \text{ V}$$

$$\Rightarrow 9 - point \text{ shifts to a new position at $G_{H}$ with}$$

$$Co-omdinates of 2.15 \text{ mA} \text{ y} 1.16 \text{ V} (2.25 \text{ mA}, 1.16 \text{ y})$$

$$\Rightarrow V_{C} C, R_{1}, R_{2} \text{ grades the above value constant.}$$

$$\Rightarrow R_{E} \text{ is Varied to set the $g$ point.}$$

$$\Rightarrow If $R_{E}$ is too large $g$ point moves in to the attend for $g_{E}$ is too large $g$ point.}$$

$$\Rightarrow T_{B} $R_{E}$ is too large $g$ point moves in to the attend for $g_{E}$ is too large $g$ point.}$$

$\varphi + 10V$ \$RC RI ZVI VBE-1 TZRE. R2 × V2 VBB design For the circuit we should know VCC., BdC. d. stange for the transistor step-I. Emittea voltage must be approximately one-tenth of supply voltage. VE = 0.2 VCC calculate RE for Ic to set up Ic Step-2  $R_{E} = \frac{r}{T_{E}} \frac{V_{E}}{T_{E}}$ Step-3 To have Q-point at mid of the DC load line, 0.5Vcc appears across collector-emitter teominals. The oremaining 0.4 Vcc peppears across the collector oresistor,  $R_{c} = 4 R_{E}$ Step-4. Design stiff voltage dividen using 100: I sule KTH < 0.01 Bdc RE . Firm voltage divider sule can be used

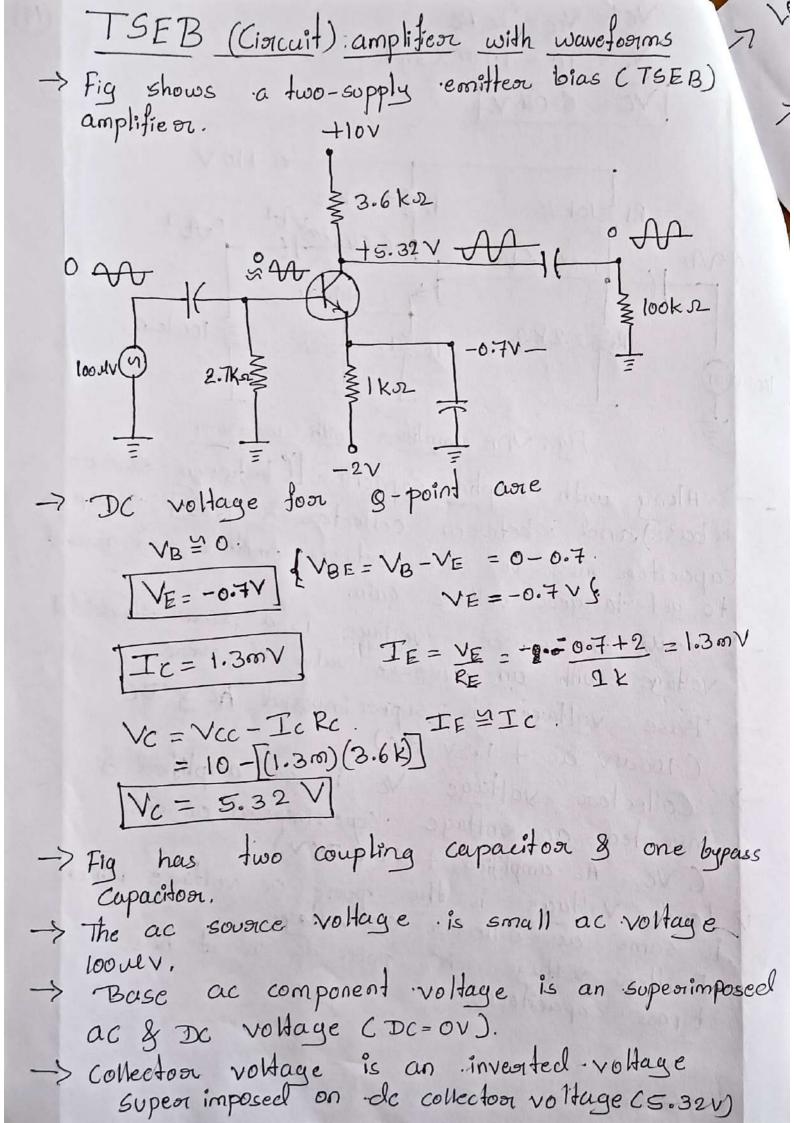

Usually Re is smaller than RI the · R2 < 0.01 Bdc RE stiff owle TR2 ≤ 0.1 Bdc RE . Fignon orule. Step -5 Finally calculate  $R_1 = \frac{V_1}{V_2} R_2$   $\frac{By \ applying \ KVL \ to BE}{TV_1 = V_{E}}$   $\frac{1}{V_2 = V_{BE} + V_E}$ 1V1= Vcc-V2 Two - Supply Emitteer Bias (TSEB) -> Some electronic equipment has a power supply that produces poth positive and negative supply Voltages. -> Fig shows a toransistoor ciorcuit with two Supplies: +10V& -2V. -> This circuit is derived from emitter bias. Fig: Two supply emitted Fig: Reclosawn TSEB Cincuit . bias. +10V. 1 + ≤ 3.6k.2 \$3.6kr \$2.7kr [+ [+ \$1kr 2.7kr L SIkr <u>-</u>2V -> Simplified TSEB is a circuit without battery -> when this type of cincuit is connectly designed, the base currorent willbe small & base voltage is ov.

The voltage acoross emitter VE -0.7V-0.7V 9 o tion RC 3.6K.2 02 -0.7V LRB LRE ZZ.7kr ZIKr D-2V (RE) is very important to find > Emitter IE 'apply ohm's law to the emitter resistor. > voltage across emitter oresistor is the difference between low negative & high negative voltage. Voltage acotoss RE ise VRE is given by VE = VRE = -0.7V - (-2V) = 1.3V. calculate IE Using ohm's law IE = VRE = 1.3 = 1.300 A. RE AY Ic ≌IE So the same current flows through 3.6 KJZ & Produces the voltage dorop that we substant forom +10V as Vc = Vcc - Ic Rc Vc= 10- (3.6 K) (1.3 mA) VC = 5.32V VCE = VC - VE VCE = 5.32 - (-0.7) VCE = 6.02V

> Two supply emitten bias also sortisfies the stiff voltage sule In In this case, simplified equations for analysis are  $V_B = 0.7 v$  apply  $kv_1$  between emitted  $T_E = \frac{V_{EE} - 0.7 v}{(-0.7 v - T_E R_E + V_{EE} = 0)}$ . ¥ RE  $V_{c} = V_{cc} - I_{c}R_{c}$ . VCE = VC + 0.7V. CVCE = VC - VE) -> Theore is a poroblem with simplified method that a small voltage acoross the base resistor. due to which a small base current flows through the resistor, a negative voltage exist between -> In well-designed circuit VB is less than -o.lv. Other types of Bias. Emitten - Feedback Bias -> In a base bias circuit like below, the ground moves all over the load line with transistor replacement y tempeorature change. +Vcc IG: VBB- VBE RB & RC RB IC= BIB IC= NCC- NCE IC= PC

Ø

> In order to stabilize the 9-point the D circuit was designed called emitter-feedback bias, emitter resistors added to the circuit. 9 truc RB ZIJ3 ZRC ICT Fig: Emitten - Feedback Fig: Emitten - FeedbackBias Fig: Emitten - Feedback Fig: Emitten - Feedback Fig: Interest - FeedbackBasic Idea. -> If Ic incoreases VE incoreases (VE=IERE) IEPIC. -> when VE increases VB also increases (VBE=VB-VE) -> Moore VB means less voltage across RB. -> Less IBN Which opposes original increase (VB=TBRB) -> It is called & feed back . C change in emitter. voltage & fed buck to base). -> It is a negative feed back as it opposes the original change in IC. -> The movement of g-point is still too large hence never became popular. > Equations for analyzing the emitter-feedback IE = VCC - VBE TC = REERET RB/Bdc IIB=IE Robe bias. VE= IERE VB = VE + 0.7V (VBE = VB - VE VB = VE + VBE) VC = VCC - ICRC

Fig: 8 point is 7 sensitive to change. Ic Fig: Example of emitteor feedback bias 430K2 \$ \$ 9102 14.9mm 9.33mA - Bdc = 300 \$ 100.52 3.25mA ---- Bdc= 100 -> Fig shows an example of an emitter - feedback bias circuit. -> Fig shows the load line and the g-point for two different curronent gains. -> A 3: 1 variation in current gain produces a large → The circuit is not nuch better than base bias. Collector - Feedback Bias. -> It is another attempt at stabilizing the g-point. -> Here voltage is feedback to the base to neutoralize the Change in IC. > If IC or incoreases; vc decoreases ( VC=VCC-ICRe) -> which decreases the voltage across base resistor. \* & decoreases IB which opposes the corginal incorease in Ic. -> It is a negative feedback. 9+400 RB ZPC Collector - feedback blas

-> Equations for analyzing collector-feedback bias 3 IE - VCC - VBE Rot RB /Bd C VB = 0.7V Vc = Vcc - IcRc. Ic 0+15V 15mA 200kr 32kr Bdc = 300 Bdc = 100. 8.58mA 4.77 mA -> Fig shows an example -> Fig shows load like Vy g-point F of collector-feedback bias. for 2 different current gains. -> 3:1 variation in current gain produces less variation in collector current than emitter - feedback, -> It is more effective than emitter - feedback bias it is simple. It g-point. Used in poraetice Collector - and Emitter - Feedback bias -> The basic idea is to use both emitted and collector feedback to tory to improve the operation. 9 +Vcc 3Rc RE -> It combines both emitteer & collector feelback bias

-> Equations for analyzing  $T_E = V_{CC} - V_{BE}$ RC+RE+RB+Bdc  $V_E = T_E R_E$  $V_{B} = V_{E} + 0.7 V$ Vc = Vcc - IcRc BJT AC models. Base biased amplifier. Coupling capaciton . . Ac short · de open y ac shart. Good coupling: Xc < 0.1R. Xc -> lo fimes smaller than R. > 50 for coupling capacitor circuit we can apply  $Z = \int R^2 + \chi c^2 = \int R^2 + (0.1R)^2 = \int R^2 + 0.01R^2 = 1.005R.$ Two approximations for a capacitor 2. Foor <u>ac</u> <u>"</u>" <u>"</u> <u>"</u> <u>"</u> <u>"</u> <u>shoorted</u>

> Fig shows a base biased Cincuit 0+30V IMNZRB Red 5KJZ +15V=12 VB= +0.7V Bdc = 100 -> as VB is small. IB can be calculated as  $T_{B} = \frac{V_{CC}}{R_{B}} = \frac{30}{1M}$ IB = 30 MA Ic = Polc IB  $T_{C} = 30 \, \text{M} \times 100$ IC IC = 3MA $V_{C} = V_{CC} - I_{C} R_{C}$ 300 = 30 - 300 X 5 k >VC ISV B VC = 15VSo, & point is located at 3mA & ISV > Fig shows how to add components to build -> base biaseel circuit as an amplifier. -0 + 30V 5KD 7Mz ₹R1= 100KJ2 100 MV G

-> A coupling capacitor used between an ac sous and the base. Coupling capacitor is open to DCT So the DC bias point, ill not change with & without Capacitor. Or 5 C -> Another coupling capacitor is used between the collector of the load resistor. -> In above fig AC voltage source is looply g it polocluces the ac base cuordent fourth) -> Total base currorent = dc component + Ac component. -> on the half cycle 30MA AAAac base current adds to dc " " > On -ve hulf cycle > This ac base current amplified by the transistor Collector terminal (as it has current gain Bdc=100.) & super imposed with dc collector current(3mA) -Total collector current = dc: Ic + Ac Ic. icq 3mA AAA -> Amplified collector current Ic flows through RC, it produces voltage across Re. when this voltage is substanced from VCC we get collector voltage VC (VCC - ICRC). VC = DC VC + AC VC. 15V NAT シモ

On the positive half cycle of ac base curront. (F)

CIB), the Ic increases & produces prove voltage across Rc. Means There is a less voltage between collector & ground hence vc is -ve.

> On the negative half cycle, Ic decrease ->

Less voltage across Rc, vc increases hence +ve.

SER AA MIM2 ° AA 0 9A +0.7V 9A 100ks Base-biased amplifier with waveforms -> source voltage is looulv.AC > It is super imposed with DC base voltage 0.7V. > Variation in VB produces variation in IB, IC -> The total collectors voltage is an inverted sine wave superimposed on de collector voltage of+15V. -> output couping capacitar blocks de component of ve & it couples ac recollector voltage (ve) to the load resistor. Load vollage is pure ac.

Voltage gain -> Av = Vout Vout = Av Vin Av=200 Vout Output voltage-s Vin = Vout Vin Av=350 Vout Av 2.5V Input voltage -> Emitten Biased Amplifien (VDB on TSEB) -> Base biased amplifier has an unstable g-point. -> Hence emitter -biased amplifier Ceither VDB or TSEB) with its stable & point is preferred. -> A bypass filter coreats ac ground without disturbing its g point. ( :Xc must be smaller than R). Grood by passing: XC < 0.1 R. VDB <u>Amplifier</u> with waveforms. -> Fig shows ·VDB amplifier. -> To calculate de voltage & current mentally open all capacitor. -> The DC values for this circuit are. The DC Vuller  $V_B = \frac{V_{CC} \times R_2}{R_1 + R_2} = \frac{10 \times 2.2}{12.2} = 1.8 V$   $V_E = V_B - V_B E (V_B E = V_B - V_E)$ VE = 1.8-0.7 VE = 101V.  $T_E = \frac{V_E}{R_E} = \frac{1 \cdot 1}{1 \cdot 1} = \frac{1 \cdot 1 \cdot 1}{1 \cdot 1} = \frac{1 \cdot 1 \cdot 1}{1 \cdot 1}$ <u>μ</u>. []IC= 1. 100 V IEMIC.

VC = VCC - LC RCVC = 10 - 1.100 X 3.6K. VC = 6.04 V anything - 0 +10V R\$ 3.6 KJZ A RISIOKIZ +1.82 +1.11 R2 \$ 2.2KD \$ 100 k-2 IKAZRE TCE Delini Fig: VDB amplifier with wavefarms -> Along with coupling capacitor [ between source & base) and c between collector & RIJ a bypa Capacitor must be used between emitter and grow to get langeon voltage gain. Mo- N > loouv ac source voltage is a small sinusoid. voltage with an average value of zero. , Base voltage is superimposed Ac & DC C100MV ac + 1.8V dc). > Collector voltage Ve is an amplified & invested ac voltage superimposed on de CVG = Ac amplified + 6.04 DCV) Load voltage is the pure ac voltage which is same as collector ac voltage. Emitter voltage is prore de as it has bypass capacitore. Cellected Vehicles in the inventee were the

Super, inspect of the she are the voltering Care

-> Load voltage is the same apti amplified (2) signal with no DC . component. > Bypass capaciton is used to incorease the Voltage gain & to maintain ac ground. Small-Signal operation. -> when an ac voltage is applied to the base of toransistor, an ac voltage appears across -> Graph is plotted VBE VSIE for analysis. Instantaneous operating point - The total base - emitter voltage of fig is an ac voltage centered on a de voltage. The size of the ac voltage determines instantaneous movement of 9 point. Langeor ac base Voltages poroduces lange variations y vice versa. TE Lonsia / los 9 an papir tisme > VBE o others eil ainr Distortion - AC IE is not same as AC VBE Positive half ac emitter current (IE) is clongated cstoretched) and negative half cycle is compressed. This storetching and componessing of AC half cycle is called distortion. Reducing distortion. -> One way of reducing the distortion is keeping the VBE as small as possible. -> Smaller the VBE smaller the IE, more linear the graph.

JEN I less than ImAp-p. IomA - --> if a the base ac voltage is a small enough sine wave, the ac emitteen cuorenent will be small sine conve with no noticeable staretching our componession of half cycle. cycle. > IE = IEg + ie IE = Total emitter current IEg = The DC emitter " ie = the ac " " > To minimize the distortion, the peak-to-peak value of ie must be small companed to IEg. Definition of Emall-signal operation is -> <u>Amplifiens that satisfy the lo pencent nule ase</u> <u>called Sonall signal amplifiens</u>. AC Beta. -> de currorent gain is the reatio of collector currorent to the debase currorent. reporesented by Bdc Bdc = Ic 1 Bre FAC ENTRE readers half a TB > ac current gain is the ratio of ac collector cuarrient to the ac base cuarrient called at AC Beta  $\mathcal{B} = \frac{\mathbf{i}_{C}}{\mathbf{i}_{b}}.$

If we plot the graph IB VS IC. we get 3 the - CA TB Ac current gain equals pratio of changes > de cusisient gain depends on the location of the 9 point. > In fig the ac signal uses only a small purid of the graph on both sides of the g-point. > Because of this, the value of the ac cuorent gain is different forom the dc cuorent gain, which uses > B equals the slope of the curve at g-point > B depends on the amount of dc collector current. te- To differentiate ac & dc quantities. ac quantities-lower to -> ie, ic, ib. letters & subscripts are used : Vbe, Vce, Veb. DC quandidies - to Upper case J JE, IC, IB letters & subscripts are used J VE, VC, VB VAE, VC, VB VBE, VCE, VCB. AC Resistance of the Emitter Diode ac memitter resistance of the emitter diode ré  $\Re = \frac{Nbe}{2}$ (ALLEROJE CHENT

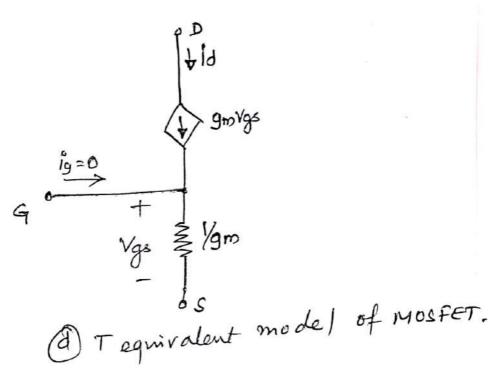

-> with solid-statezen calculus, it is one is n given by  $\int \Re = \frac{25mV}{TE}$ ~> re' determines the voltage gain, Two Toransistoor Models > Toransistoor model is an ac equivalent circuit ofor > totansiston. used to analyse ac operation of a totansiston there are two totansiston models. with so help side of 1. Tmodel 2. TT model. T-model (Ebeas-Moll model). -> One of the eagliest model. -> called as Ebeors - molt model also. -> The name T is used as it has T shape 1 tic ore chraughter ib. Dic n P => ~ Jo îв. 0— Lie lip. -> The model circuit looks as in fig. -> the emitter diode of a toransistor acts like an ac resistance (re') -> collector diode act like a current source (ic)

by when analysing a toransistor amplifier, we . 3 can replace each transistor by T-model and cakulate the value of re' and other ac quantities. as ie = ic ! Zin Chase =  $\frac{1}{16} \frac{1}{316} = \beta \pi e^{1}$ B-> cuorsient gain -> Input impedance of the base is equal to the ac current gain times the ac presistance of the emitten diode. 2. II- model. -> It is the violant representation of Zincbuse) -> It is easy to use than the T-model because input impedance is seen clearly in TI model. Buli dic -> most of the time . IT model is used for anelysis.

Analysing an amplifier. -> Amplifier analysis is complicated because 7 both de 8 ac sources ave available in the same cincuit. -> To analyse on amplifien we have to calculate the effect of dc sources and ac sources sepen -ately & then find the total effect by Super position theorem. 2. DC Analysis > Dc. analysis calculate the dc voltages & Cuardients like NBE, IB, IC & VCE -> To doraw the Dc equivalent cincuit open all the capacitors. Then the remaining circuit is known as DC equivalent circuit of of an amplifie or. AC Analysis -> Ac analysis is done after de analysis. > To cloraw an AC equivalent cioncuit Joron a given amplifiese shoot cioncuit all the capacitos and the DC voltage source is shorted circuited

to ground & replace the toransistor with ac equivalent circuit. Thoree steps for ac equivalent circuits are i. short all capacitors ii. Dc supply grounded iii. Replace the toransistor by its TT or T model. Draw the ac equivalent circuit.

I. Base - Blased amplificer. CCE amplifier) (27) -> Fig shows base - biased amplifien & its ac equivalent circuit. ZRB ZRC Vin RL VIN RB RB ERCERL (a) To get ac equivalent cioncuit, shoort all capacitors & de voltage sources. connect vec to goround. -> Toronsistor has been replaced by its TI model. ic is the output cuorent thorough RellRL. -> Vin appendis acoross RB Il Borel -> II VDB amplifier. CCE amplifier). > Fig shows VDB amplifier & its equivalent circuit. -otvcc RIZ ZRC  $V_{in} \bigoplus_{i=1}^{R_2} R_{i} \bigoplus_{i=1}^{R_2} V_{in} \bigoplus_{i=1}^{R_2} M_{in} \bigoplus$ (a) (b). -> Ac Voltage appears acoross RI 11R2 11 Bore -> ic joumps through RCIIRL

TSEB amplifier -> Fig shows TSEB amplifien & ac equivalent circu = Vin B RB RET VIN B RB BBRE Dic BRC RL -> Ac input voltage appears across RB 11. Bore -> The currorent source pumps on ac currorent of ic through RcIIR2. Acquantities on the Data sheet. H parameters - when the toransistor was 1st invented, an approach known as the h parameters was used to analyze & design teransistor clarcuits. -> It This method models the torunstistor on what happening at its teorminals without regard for the "physical process inside. hje - Input impedance small signal- current gain > Four h parameters are. hie - Input impedance hore - voltage feelback ratio hoe - · output admittance

in the second second

dynamilt

Relations between R&H passameters hfe? small signal current gain is identical to the ac current gain B = hfe hie -> input impedance is equivalent input impedance of ste passameter to the -> re = <u>hie</u> > hore & hoe are not needed for touble shooting and basic design. Voltage complifieors Voltage gain - It is the statio of ac output voltage by the ac input voltage. with this concept another equation for voltage gain for torouble shooting. Voltage gain. I. Desilved form the II-medel. Fig shows (VDB) amplifien & its equivalent circuit ~ with TT model. \$RC RIZ R2 Vout Vin @ Ri = Rz = = Pone Dic = Rz Vout REST (VOB) CE amplifieor. ac equivalent circuit with Trodel

⇒ The ac base current (ib) flows through (Bore) T

according to ohm's law.

$$\forall in = ib Bore'$$

$\bigcirc$   $\bigcirc$

⇒ The current pumpus an ic through the (Rell R\_1)

$\therefore$  Vout = ic (RellR\_1) = ic  $\cong pib$ .

$form \bigcirc g \in pib (RellP_1) - (2)$

$Av = Vout = Pib (RellP_1) - (2)$

$Av = Vout = Pib (RellP_1) - (3)$

$Av = RellR_1$

$g = RellR_1$

$g = RellR_1$

$equation (3)$  can be written as

$Av = \frac{gre}{2te^2}$

$\Rightarrow$  The voltage gain equals the ac collection

$gresistance divided by the ac presistance of emilten

$digde ain ain form the T modelt$

$T. T. Destived form the T model t

$\Rightarrow$  Fig shows ce amplifien g ac equivalent circuit with Tmodel

$R_1 = \frac{gre}{2te^2}$

$CE amplifient ac equivalent circuit with Tmodel$$$

(31) > Vin appears across . re! Vin = leste > collector circuit pumps ic through ac collector resistor nc 976 = RellRL · · · Dout = · ic nc Just's cont  $A_V = \frac{.90ut}{.9in} = \frac{.ic}{.91c}$  .ic = ie $A_{19} = \underline{31c}$ -> Both models gives the same equations The Loading effect of input impedance. -> Ideal ac voltage source has zero source resistance.

We have an amplifien cincuit which necluce the appears across emitted cinput) diode. > Fig shows CE amplifient cincuit, ac equivalent cincuit & effect of input impedance. 50, 50, ZRI ZRC ZBIE Dic ZRC ZRL ZRL Ration SR2 Vg Zincstate Zincbase Freshered ac equivalent circuit = CE amplifier circuit Ra ZinEstage) Vin Vg () effect of input impedance

> Vg (generration & source) Voltage) -> Vy has an internal resistance Re. > when a generator (source) is not stiff some of the ac source voltage is doropped acouss RGL > As a gresult ac voltage between base & ground is less than ideal. -> AC generator (Vg) has to drive input impoddance of the stage Zincstage). -> Tota' Zin Cstage includes effect of RI 11R2 HI Zin (base) Einput impedance of the base] -> ... The input impedance of the stage equals Zin (stage) = RI 11R2 / B91e' Input voltage -> when Vg is not stiff; Vin < Vg foot voltage divideor bitheorem we can worite Vin = Zincstage) Vg Rer + Zincstage) Ug = Zincstage) Vin CC amplifieor -> when RL is sonalless the Rc, the voltage gain of a CE stage becomes small & amplifier may become overloaded. -> To avercome forom this poroblem CC on emitter follower is used > Fig shows an emitter follower. Collector is at a ground. Input is given to the base tearminal output is collected acoross the emitter teaminal.

> Fig shows emitteer follower circuit with weveform.

+Vcc Vin@ 3R2 ZRL ZRE -> Fig shows total voltage between emitteer & ground. -> Fig shows total voltage ac input is centered on great between base & grand which is actdc. VEA 1 by by VBA VEG FAR-VBgt-f > t. > t -> Fig shows collector -> Fig shows ac emitter Vollage. since there is voltage coupled to load. no resistor Vc = Vcc >It is inphase & became amplitude Voul ~ 0/P fottows i /P (voltage follower) pve Vac ---allin's Arbing V.U >t -> capacitor blocks dc. -> Negative feedback is used by emitted follower. -> Ac emitter resistance. JOLE = RE 11R2 . [diffeorent forom internal > Consider the ac equivalent with T model of conitter follower circuit.

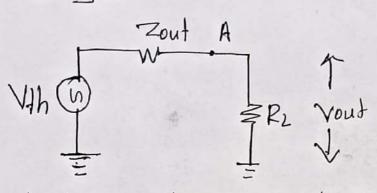

Output Impedance -> Output impedance of an amplifier is the same as its the venin impedance. > Advantage of an emitter follower is its low operput impedance. Maximum power · toranster · occurs · when load impedance & = source (therenin) impedance. to the output impedance to the outp. of an emitteen follower. Fig shows an ac generator driving an amplifier. , if the source is not stiff, some of the ac voltage is doupped accross the integral resistance RG. Vg Q Amplifier ZRL In this case we need to analyze the voltage divident shown below to get input voltage Vin ) Zin Vin Ng G Same idea can be used at output side of the Apply Theirenin Theorem at the load terminals. Amplifien <= =RL In the venin equivalent ciacuit, zout impedance comme a voltage divideor with RL, as in fig. forms

Ville FRL Vout > if zout is much smaller than R2, the output source is stiff & vout = Vth. CE Amplifien. > Fig. shows the ac equivalent circuit for the output side of CE amplifies. ico FRC FR2 > Affer applying therenin theorem circuit becomes Vth Q RL Vous -> The output impedance facing the load resistance is Rc. -> voltage gain of CE amplifies depends on Re a decigneer cannot make Rc too small without loosing voltage gain. Because of this, CE amplifieers are not suited to driving small load resistances. Emitter follower - + VCC PROCEERS Win ZR2 ZRE ZR2 Fig: Ac equivalent ciorcuit Fig: Emitten ton emitten follower. follower.

A, we get the venin's theorem to point 3

→ The output impedance zout is much smaller than you can CE amplifier. It equals Zout = REII (ret + <u>ReIIRIITR2</u>)

→ The impedance of Base is ReILRIITR2

→ Custant gain of the totansistor reduces impedance by B.

-> Ideal action - In some designs the biasing oresistance & ac oresistance of the contited diade become negligible.

Zouf = <u>RG</u> B B follower allows us to build stiff ac sources.

Instead of using a stiff ac source that muximizes the load voltage i,e Zouf << RL c stiff voltage source).</li>

-> A designer may jorefer to maximize the load power. Zout=RL ( Maximum power toranster)

> In this way, emitter follower can deliver maximum power to a 'low-impedance 'load such as sterrospeaker. > If we remove RL, circuit acts like a buffer between input & output.

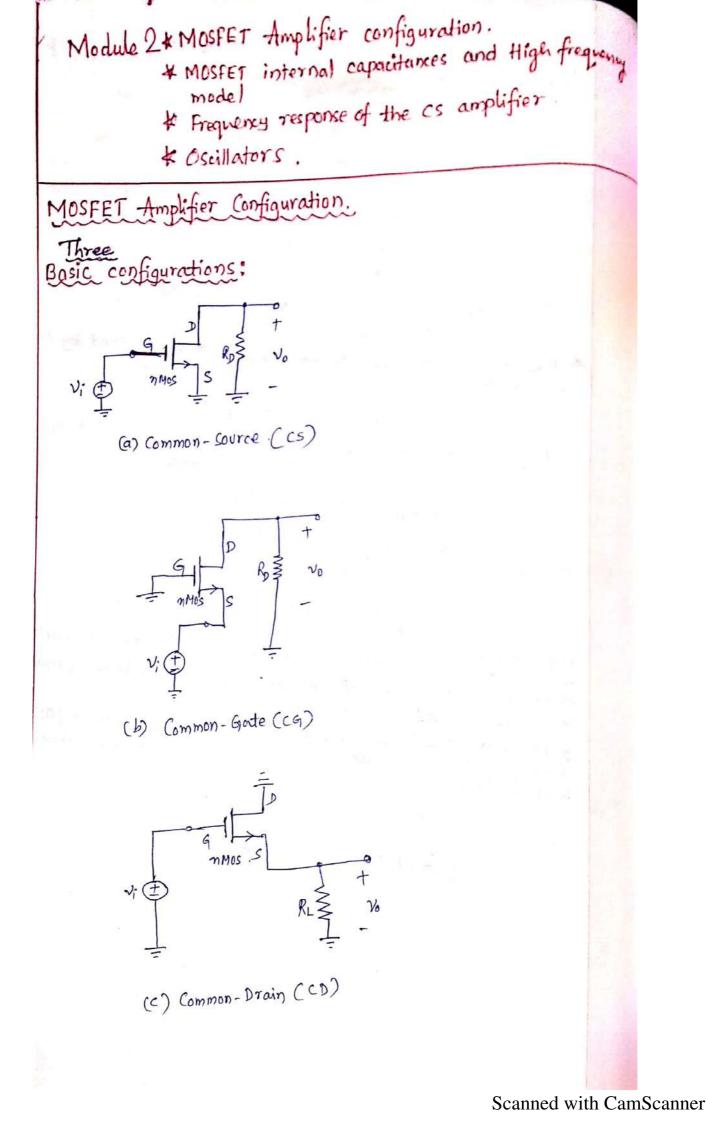

Biasing in MOS amplifier Circuits.

\* Essential step in the design of a MOSFET amplifier circuit is establishment of an appropriate dc aperating point for the transistor. (this is known as biasing)

\* An appropriate de operations point is characterized by a stable and predictable de drain current ID and by a de drain-to-source voltage Vos that ensures operation in saturation region for all expected input-signal levels.

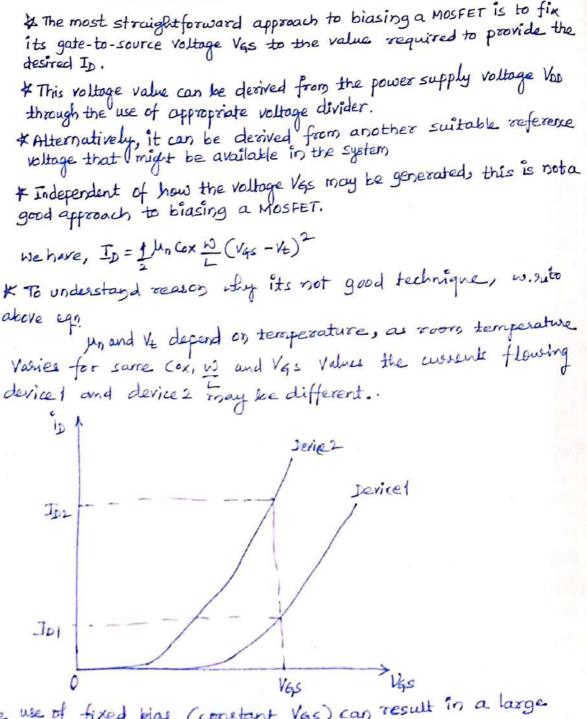

# (I). Biasing by fixing Vas.

The use of fixed blas (constant Vgs) can result in a large variability in the value of .D. Devices! and Devices? represent extremes among units of same type

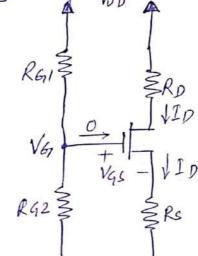

(1) Biasing by fixing Vq and connecting a Resistance in the source + An excellent biasing technique for discrete MOSFET circuits of fixing the dc voltage at the gate, Vq, and connecting a resistance in the source lead,

D Device 2 LID Jevicet Slope = - 1/Rs Rs ID2 Ipi VESI Basic Arrangement. V652 . (a). Biasing using fixed voltage at (b) reduced variability in is the gate VG, and a resistance in the For this circuit we can write, Vg = Vgs + Rs. ID \* Now, if Vg is much greater than Vas, ID will be mostly determined by the \* However, even if VG is not much larger than VGS, resistor Rs provides regative feedback, which acts to stabilize the value of bias current ID. \* VG = VGS + RSID equation indicates that since VG is constant, Vas will have to decrease. This inturn results in a decrease in I, a change that is opposite to that initially assumed. Thus the action of Rs works to keep ID as constant as possible. \* The negative feedback action of Rs gives it the name degeneration I). Biasing Using a Drain-to- Gate feedback Resistor \* Here the large feedback resistance RG (in MSL range) forces the dc veltage at the gate to be equal to that cit the drain (because IG=0). Thus RD we can write,  $V_{ejs} = V_{DS} = V_{DD} - R_D I_D$ . +ID which can be recorded in the form RG w - ID VOD = VAS + RD ID # Thus here to ID changes, Vas say increases, Vies must decrease \* This decrease in Vass in turn causes a decrease in ID, a change Biasing the MOSFET Using a i.e opposite to in direction to the large drain-to-gate feedback one originally assumed resistance, RG

Note :

& Thus the negative feedback or degeneration provided by Rg works to keep the value of Jo as constant as possible

& The above circuit utilized as a CS amplifree by applying input voltage signal to the gate via coupling capacitor, so as not to disturb the dc bias conditions already set up or established.

# The amplified output signal at the drain can be coupled to another part of circuit, again via a capacitor.

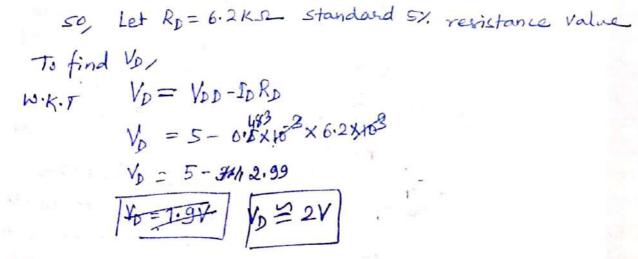

Example 1: It is required to design the circuit as shown below to operate at a de doain current of 0.5mA. Assume Vio=+5V. Kn W/L=1mA/12  $V_t = IV$  and  $\lambda = 0$ . Use a standard 5% resistance value for RD, and give the actual values obtained for ID and VD.

Solution

Given ID = 0.5 mA data VGS = VDD - JD RD = 15 20:5×103 RE.  $R_{D} = \frac{V_{DD} - V_{GS}}{I_{D}} = \frac{5 - 2}{0.5 \times 10^{3}} = \frac{3}{0.5 \times 10^{3}} = 6 K_{-}^{-1}$ To find Vqs,  $I_D = \frac{1}{2} \mu_n \cos \frac{W}{L} (V_{qs} - V_t)^2$ 0.5×103×2= 1×10 V45-1)2  $V_{45-1} = 1$

> Vas=2V ~ substituting this value in above eqn. to find Rp wegel RD=6KJ2

new value of ID will be

$\frac{T_{D} = V_{DD} - V_{4S}}{R_{D}} = \frac{5 - 2}{6 \cdot 2 \times 10^{3}} = \frac{3}{6 \cdot 2 \times 10^{3}} = 0.483 \text{ mA}$

Evende: It is required to design the circuit of shown below to establish a dc drain current  $I_D = 0.5 \text{ mA}$ . The MOSFET is specified to have Vt = 1Vand  $K'_N W/L = 1 \text{ mA}/v^2$ . For simplicity, neglect the channel length modulation effect (i.e assume  $\lambda = 0$ ). Use a power-supply  $V_{DD} = 15V$ . Calculate the percentage change in the value of ID obtained when the MOSFET is replaced with another unit having the same  $K'_D W$  but Vt = 1.5V.

solution :

5

\* As a rule of thumbs for designing this.

biasing circuit, we choose RD and Rs to provide one-third of power-supply voltage VDD as a drop across each of RD, the transistor Ci.e VDS) and Rs.

# For VDD=15V, this choice makes.

\* VDD=15V, and VS=+5V, since ID

required to be 0.5mA, we can find values of RD and Rs as follows:

$$R_{p} = V_{00} - V_{0} = 15 - 10 = 10 \text{ K} = 10 \text{ K$$

$$R_{s} = \frac{V_{s}}{R_{0}} = \frac{5}{0.5 \times 10^{3}} = 10 \text{ K}.\Omega_{-}$$

The required value of Vas can be determined by first calculating the overdrive voltage Vor from To al K. (W) (Vac-Vt)<sup>2</sup>

$$I_{D} = \frac{1}{2} K_{n} \left(\frac{W}{L}\right) \left(v_{4s} - v_{L}\right)^{2}$$

$$0.5 \times 10^{58} = \frac{1}{2} \times 1 \times 10^{58} \times \left(v_{4s} - v_{L}\right)^{2}$$

$$\left(\frac{V_{4s} - 1}{2}\right)^{2} = 1$$

$$\frac{V_{4s} - 1}{\sqrt{4s^{2} - 2V}}$$

$$\frac{1}{\sqrt{4s^{2} - 2V}}$$

$$V_{5} = +5V, \quad V_{5} \text{ musf be}$$

$$V_{6} = \sqrt{s + \sqrt{6}} s = 5 + 2 = 7V$$

\* To establish this voltage at the gate we may select Rai= 9M\_2 and Raz=7M.2.

\* Observe that the dc voltage at the drain (+10V) allows -for a positive signal swing of +5V(i.e up to Voo) and a negative signal swing of -4V [i.e down to (Vg - Vz)]

& If the NMOS transistor is replaced with another having Vt=1.5V, the new value of ID can be found as follows:

$I_{D} = \frac{1}{2} \times 1 \times (V_{45} - 1.5)^{2} - 0$ From current equation . · As

We know that Vg = Vgs + IDRs

7 = VGS + 10 Ep V45=7-10Ip -2 :.

If we substitute in equ () fled Vas from eqn (2) we get

$$I_{D} = \frac{1}{2} \left( 7 - 10I_{D} - 1.5 \right)^{2}$$

$$2 I_{D} = (5.5 - 10 I_{D})^{2}$$

$$3 I_{D} = 5.5^{2} + (10 I_{D})^{2} - 2 \times 10 I_{D} \times 55$$

$$3 I_{D} = 5.5 + (10 I_{D})^{2} - 2 \times 10 I_{D} \times 55$$

$$3 I_{D} = 5.5 + (10 I_{D})^{2} + 30.25 - 110 I_{D}$$

$$10 I_{D}^{2} - 112 I_{D} + 30.25 = 0$$

$$I_{D} = 5.5 + I_{D}^{2} - 1.12 I_{D} + 0.3025 = 0$$

$$I_{D} = 5.5 + I_{D}^{2} - 1.12 I_{D} + 0.3025 = 0$$

$$I_{D} = 5.5 + I_{D}^{2} - 1.12 I_{D} + 0.3025 = 0$$

$$I_{D} = 5.5 + I_{D} = 0.455 - 0.5 = -0.045 \text{ mA}$$

$$I_{D} = 0.455 - 0.5 = -0.045 \text{ mA}$$

$$I_{D} = 0.455 - 0.5 = -0.045 \text{ mA}$$

$$I_{D} = 0.5 + 100 I_{D} = -57. \text{ charge}$$

1.0

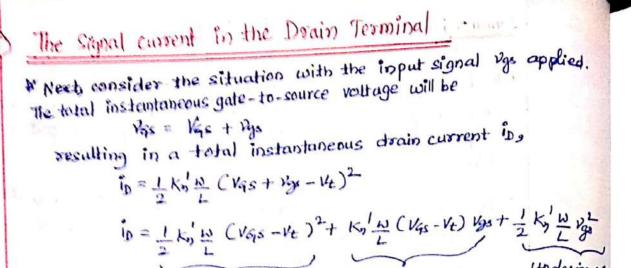

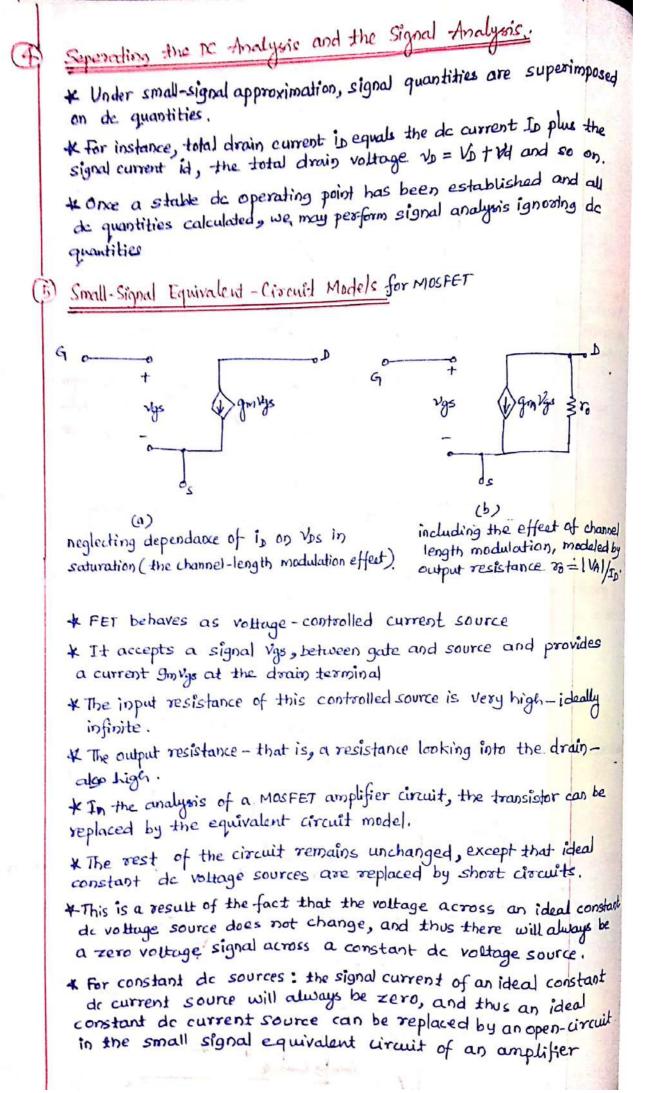

Small-Signal operation and models

K the large-signal operation of common-source MOSFET complifier, linear amplification can be obtained by biasing the MOSFET to operate in saturation region and by keeping input signal gnall.

\* To study small-signal operation in some detail, we utilize. conceptual common-source amplifier circuit

·Vo

A VOD

fig. conceptual - circuit \* Here Mos transistor is biased by applying a dc voltage Vas, & Imput signal to be amplified us is shown superimposed on the dealer with the dealer.

The DC bias point

The DC bias current ID can be found by setting

$$V_{gs} = 0$$

; thus

$\frac{1}{2}$  The dc bias current ID can be found by setting  $V_{gs} = 0$ ; thus

$I_D = \frac{1}{2} K_D \frac{10}{2} (V_{qs} - V_{\pm})^2$

where we have neglected channel length modulation \* The de voltage at the docuin, Vos or simply Vo (since s is grounded), will be

1

\* To ensure saturation-region operation, we must have

K-Furthermore, since the total voltage at the drain will have a signal component super-imposed on Vo. Vo has to be sufficiently greater than (Vgs-VE) to allow for the required signal swing.

De bias current current & 2gs

component, it represents non-linear distortion.

\* To reduce the non-linear distortion introduced by MOSFET, the input signal should be kept small so that

resulting in

or equivalently, Vys << 2 Vor. where Vov is the overstrive voltage at which transistor operating. \* If the small-signal condition is satisfied, we may neglect the last term & express is as

where

ip = Ip + id id = Kn 10 (Vas - Ve) Vac

\* The parameter that relates 1d and Vgs is the MOSFET transcordud nce

-nce, 9m

$$g_m \equiv \frac{id}{v_{qs}} = \kappa_0 \frac{N}{L} \left( v_{qs} - V_E \right) \quad \text{or} \quad g_m = \kappa_0 \frac{W}{L} \quad V_{0V}$$

\* Note that gm is equal to the slope of the ip-Vgs characteristic at the bias point,

$$am \equiv \frac{\partial I_D}{\partial N_{qs}}$$

|  $V_{qs} = V_{qs}$ .

Scanned with CamScanner

Scanned with CamScanner

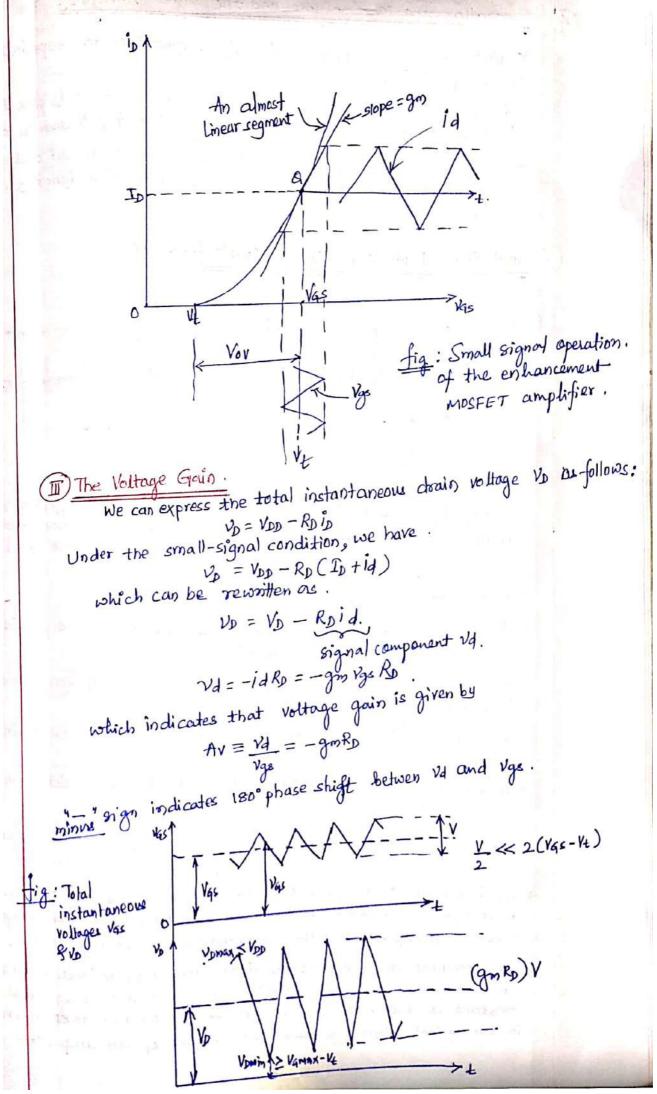

( The Transconductance 9m

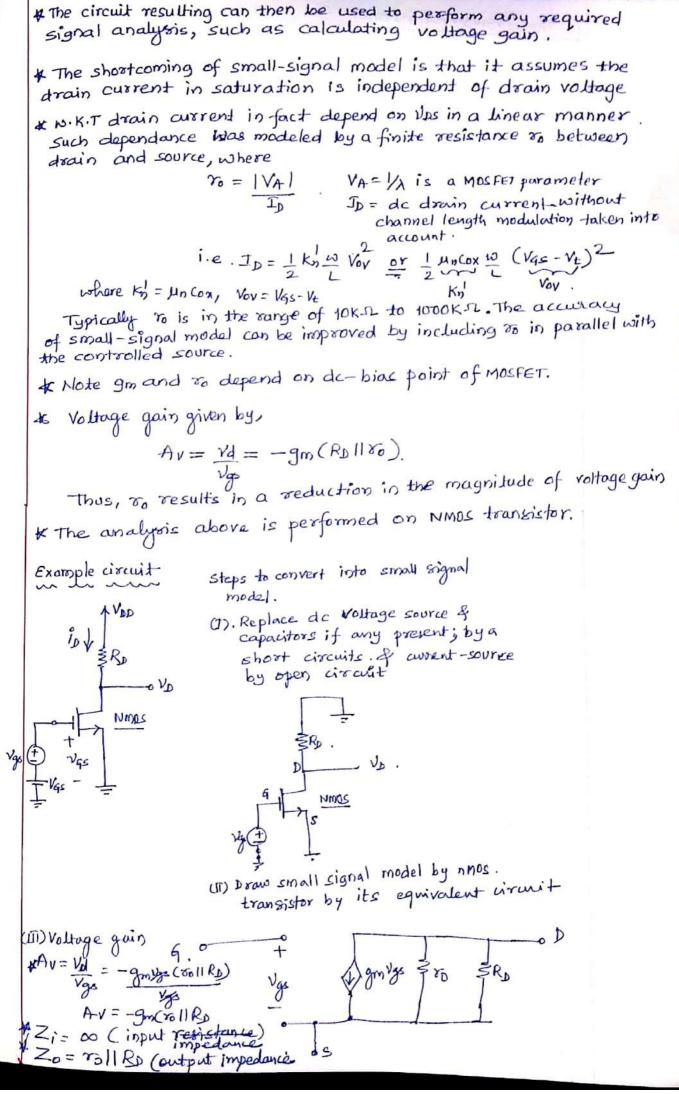

4 We shall now take a close took at the MOSFET transconductors given by, gm = Kn W (Vgs-VL) = Kn W Vor where Vor = Vgs-Ve

Note: MOSFET saturation current is given by ID = 1/K = (1/5-1/6)2

gn =  $\frac{\Delta I_D}{\Delta V_{45}}$ , i.e differential expression for ID W.T. t Vas we get

$$g_{m} = \frac{A I_{D}}{A V_{4s}} = \frac{1}{2} K_{s} \frac{W}{L} Z (V_{4s} - V_{c}) (1 - 0)$$

$$g_{m} = K_{m} \frac{W}{L} (V_{4s} - V_{c})$$

# Trans - I'm is directly proportional Kn = un Cox and W/L ratio of Mes conductonce

& Also, observe that for a given device the transconductance is proportional to the overdrive voltage, Vor = Vas - VE, the amount by which the bias velta Vas exceeds the threshold voltage VE.

\$ Note: However, that increasing gm by bigsing the device at a larger 1/45 has the disadvantage of reducing the allowable signal swing at the drain.

# Another useful expression for gm can be obtained by substituting for (VGS-VE) by  $\sqrt{2I_0}/K_0^{\prime}(\frac{\omega}{L})$  we get we have,  $g_m = K_0^{\prime}\frac{\omega}{L}(V_{4S}-V_E) = K_0^{\prime}\frac{\omega}{L}\sqrt{2I_0}/K_0^{\prime}\frac{\omega}{L}$

gm = V2Kin VW/L VID.

This expression shows that 1. For a given MOSFET, gm is proportional to the square root of the dc bias current. 2. At a given bias current, gm is proportional to  $\sqrt{\frac{w}{L}}$

Scanned with CamScanner

olution

We first evaluate the dc operating point as follows:

$I_0 = \frac{1}{2} \times 0.25 \times 10^{-3} (V_{GS} - 1.5)^{2}$

of For simplicity, we have neglected the channel-length modulation (1=0) Since the dc gate current is zero, there will be no dc voltagedrap across Rg: thus Vas = 16.

$$I_{D} = 0.125 \times 10^{-3} (V_{D} - 1.5)^{2}$$

Also,

$V_D = V_{DD} - I_D R_D = (15 - 10 \times 10^3 I_D).$  $I_{p} = 0.0125 \times 10^{-3} (15 - 10 \times 10^{3} I_{p} - 1.5)^{2}$  $8 \times 10^3 f_D = (13.5 - 10 \times 10^3 f_D)^2$  $8 \times 10^{3} I_{D} = (3.5)^{2} + (0 \times 10^{3} I_{D})^{2} - 2 \times 13.5 \times 10 \times 10^{3} I_{D}$  $0 = 10000 I_0^2 + 13.5^2 - 262 \times 10^3 J_0$ ID=1.06mA & VD=4.4V Solving . ( Note: that other solution of quadratic equation is not physically meaningful.) \* The value of gm is given by, gm = Kn in (V45 - V2) gm=0.25×103(4.4-1.5)

\* The output resistance To is given by, To = VA = 50 = 47KA

gm = 0.725 mA/V

Vo = - govy (RDIIRLIIVO) × Since Mg=Vi, the voltage gain Av = - gm (RollRL1126) = -0.725×103 (10×11 10×11475) Av= -3.3V/V .

Y To evaluate the imput resistance Rin, we note that the input current i is given by,  $i_{l} = (v_{i} - v_{o})/R_{q}$  $\frac{1}{R_{c}} = \frac{V_{i}}{R_{c}} \left(1 - \frac{V_{o}}{V_{i}}\right)$  $\begin{aligned}

&i_{i} = \frac{V_{i}}{R_{G}} \left( 1 - (-3 \cdot 3) \right) \\

&i_{i} = \frac{4 \cdot 3}{R_{G}} \frac{V_{i}}{R_{G}}

\end{aligned}$ Thus,  $Rin = \frac{Vi}{I_1} = \frac{R_6}{4.3} = \frac{10 \times 106}{4.3} = 2.33 M.O.$ # The largest allowable imput signal vi is determined by the need to keep MOSFET in saturation at all times; that is, Enforcing this condition, with equality, at the point vas is maximum and vos correspondingly minimum, we cosite Vosmin = Vasmar - Vt. Vas - lAv Vi = Vastvi - Ve.  $4.4 - 3.3 \hat{V}_i = 4.4 + \hat{V}_i - 1.5$  $\hat{V}_{i} = 0.34 Y$ . Hote that : in the negative direction, this input signal amplitude results in Vienin = 4.9-B.34 = 4006V, which is larger than VE. IF Thus, as the limitation on input signal amplitude is posed by the and thus transistor semains conducting. upper-end considerations, and the maximum allowable input signal peak is 0.34V \* End of Module 1.

. . .

1

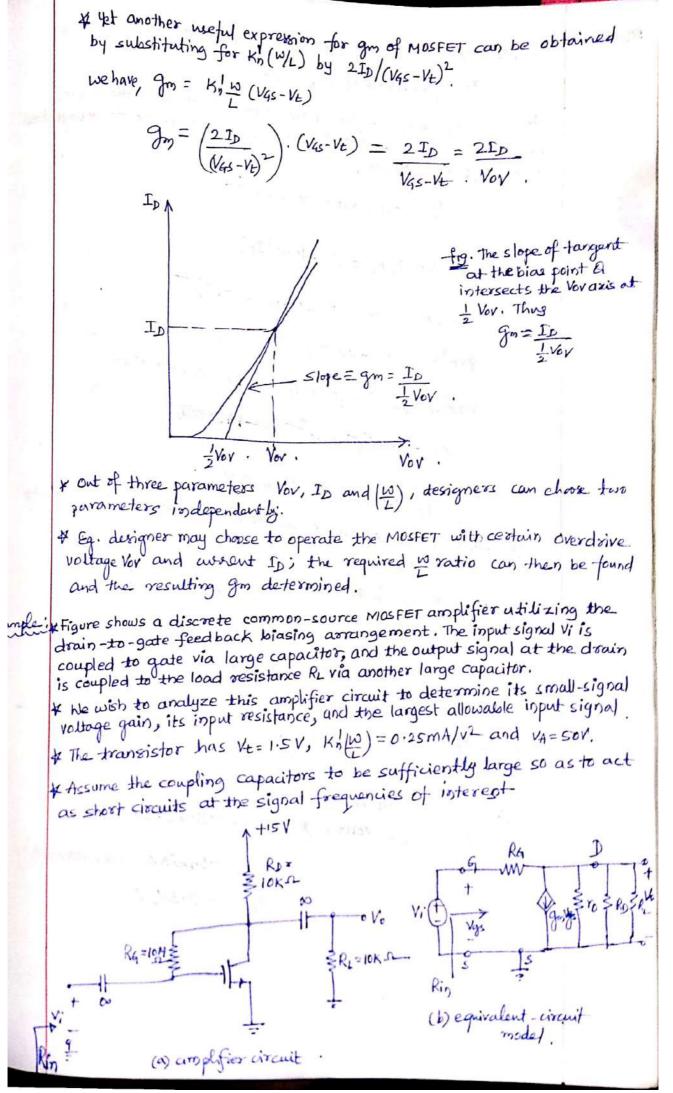

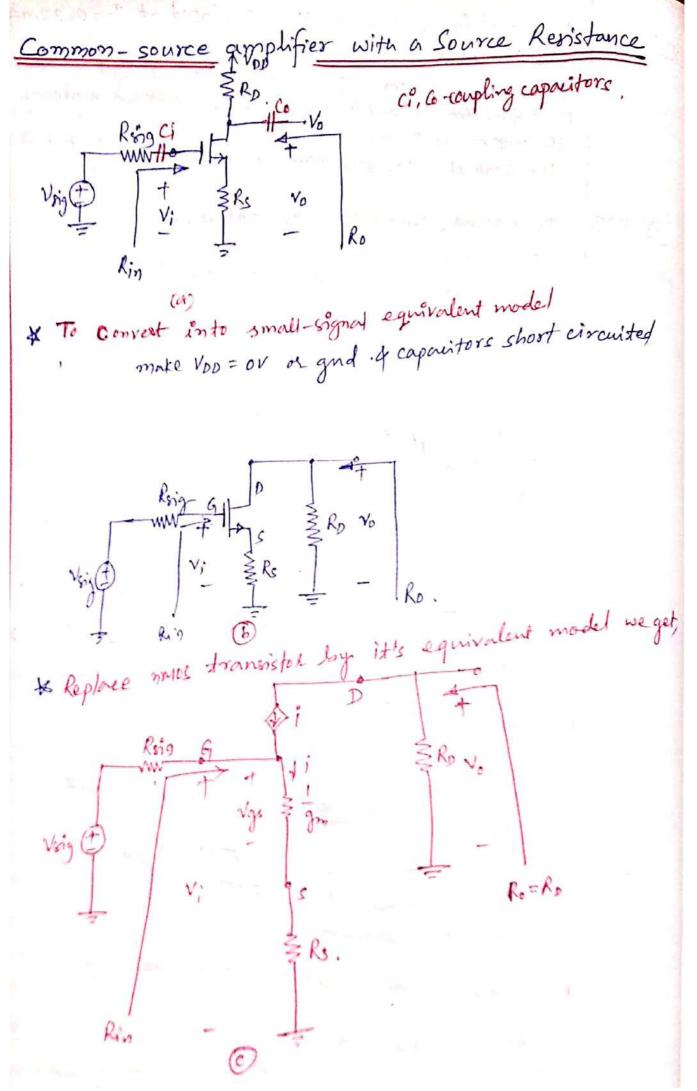

The Common - Source Amplifier without Rs (source resistance) \* Common - source configuration is most widely used mos amplifier. configuration. ignito is & de & de supply Risg ERD VO & re trainen the ctt we get fige Ving ( bioring fig@ Common-Source (cs) amplifier fed with signal Vsig from generator with a residence Rein The fed with signal Vsig from generator with a resignance Rig. The bias circuit is omitted. Rag A gm vgs ZKS Vgs= Vi Ro = RD1120 fig (b) The common-source amplifier with the MOSFET replaced with its. hybrid-IT model. Input Revistance, Rin = 10. If The output voltage Vo is found by multiplying the current (gm Vgs) by the total resistance between the output node Vo = - (9m Vgs) (RD || BC) & ground,. Since vgz=Vi, the open circuit voltage gain Ave = 1/2 can be obtained ore, Avo = -gm(RD1100) # ro, reduces the voltage gain. In discrete-circuit amplies, Ro is much lower than roy and the effect of ro reducing Ard & Thus in many cases we can neglect to and express Avo simply  $a_1$ , Avo = (-9mRp)Neglecting to is allowed in discrete - circuit design only.

Scanned with CamScanner

4 The output resistance Ro is the resistance seen looking back into the output terminal with vi set to zero. \* We see from fig. I that with Vi set to zero, Vgs will be zero & thus grovings will be zero, resulting in  $R_0 = R_D || r_0$ tiere, To has the beneficial effect of reducing the value of p & In discrete circuits, this effect is slight & we can make the approximation. Ro = RD Observations :=> 1.\* The imput resistance is ideally infinite. 2. & The output resistance is moderate to high. 3.7 The open-circuit voltage gain Aro can be high, making CS configuration the work-horse in Mos amplifier design. However bandwidth is less in cs configuration. Overall voltage gain Gv = Vo = Vo Vi Vgs & Infinite Rin will make entire signal isig appear at the amplifier input, Vi= Vsig. \* If a load registance RL is connected to the output derminal of the amplifier, this registance will come in parallel with Ro. \* Voltage gain Av = - gm (roll RollRL) \* Overall voltage gain Gy = Av because in this case VsigeVi 50 GV = - gm ( rollRD 11RL ) By Replaning foig) G Vopto zero Congado We get Noise Nigs = Vi D grings gro We get Noise J - Vo equipolet circm. Circuit including Re

# It should be noted that we have not included to in the aquivalent circuit model to simplify analysis, & effect of no on edicates circuit amplifier is not important

$$R_{in} = Q$$

# from fig. input revisitance Rin is infinite and thus  $V_1 = V_{in}$  g

# there frontion of  $V_1$  appears between gale  $\gamma$  source as  $V_{gs}$ .

# The can be determined from Voltage divider composed of  $V_{gn}$

and Rs. that appears across the amplifier import as follows.

$Mg^s = \frac{V_1}{V_{gm} + R_s} = \frac{V_1}{1 + g_m R_s}$ .

# Note: We can use of the value of Rs to control magnitude of

$V_{gs}$  & thereby ensure  $V_{g}$  doesnot become two large, and cause

unacceptably leigh non-linear distortion.

# One more advantage of Rs, is it increases allowable boundwith.

of import signal.

# The output values of Rs, is it increases allowable boundwith.

$V_0 = -(\frac{V_1}{V_{gm} + R_s})$  Rs.

$V_0 = -(\frac{V_1}{V_{gm} + R_s})$

Notice current i by Rs.

$V_0 = -Rs$ .

$V_0 = -(\frac{V_1}{V_{gm} + R_s})$

$V_0 = -(\frac{V$

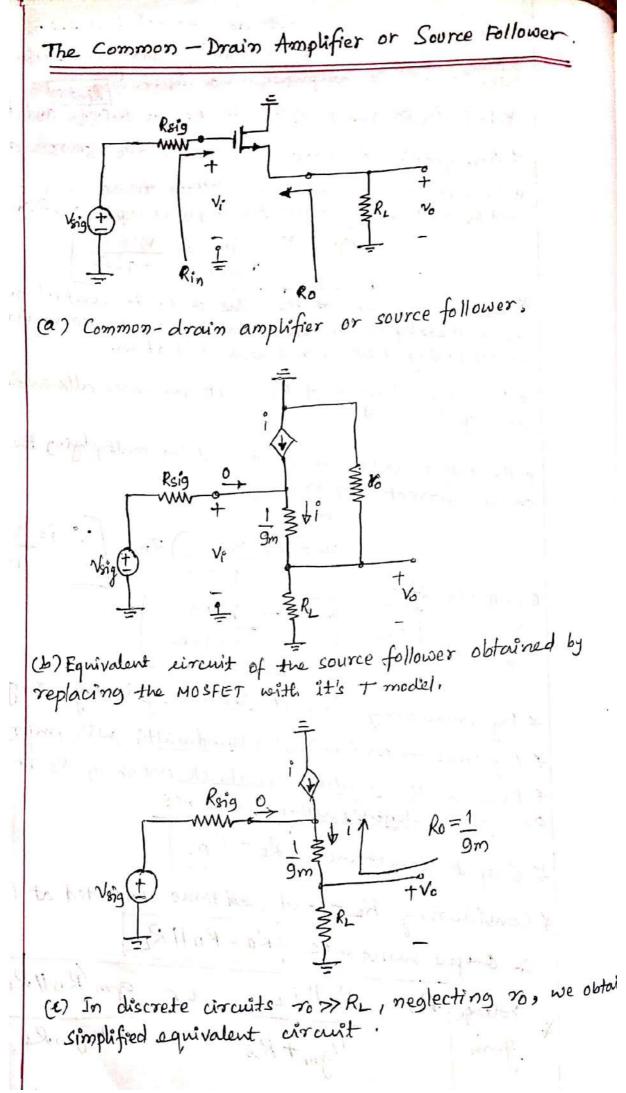

\* The source-follower is fed with a signal generator and has , a RL between source terminal & ground. \* RL includes both actual load and any other resistance that may be present between a source terminal & ground. \* T model is more convenient to use as RL is go connected in source terminal. \* Rin= 00. and  $AV \equiv \frac{V_0}{V_i} = \frac{R_L}{R_L + 1/g_{min}}$ setting RL= 00 we obtain. Avo=1. # The output resistance Ro is found by setting Vi= 0 (i.e by grounding gate). 4 Ro=1/gm, Looking back into output terminal, excluding RL \* The unity open-circuit voltage goin together with Ro can be used to find when a load resistance RL connected. \* Because Pin=10, Vi= Vsig, and the overall voltage gain is.  $G_V = A_V = \frac{R_L}{R_L + 1/gm}$ Ygm is usually low, so Gv ≡ 1 (unity gain) ~ \* Very high input resistance (ideally to) \* Low output resistance & \* open-circuit voltage gain near unity (ideally, unity)

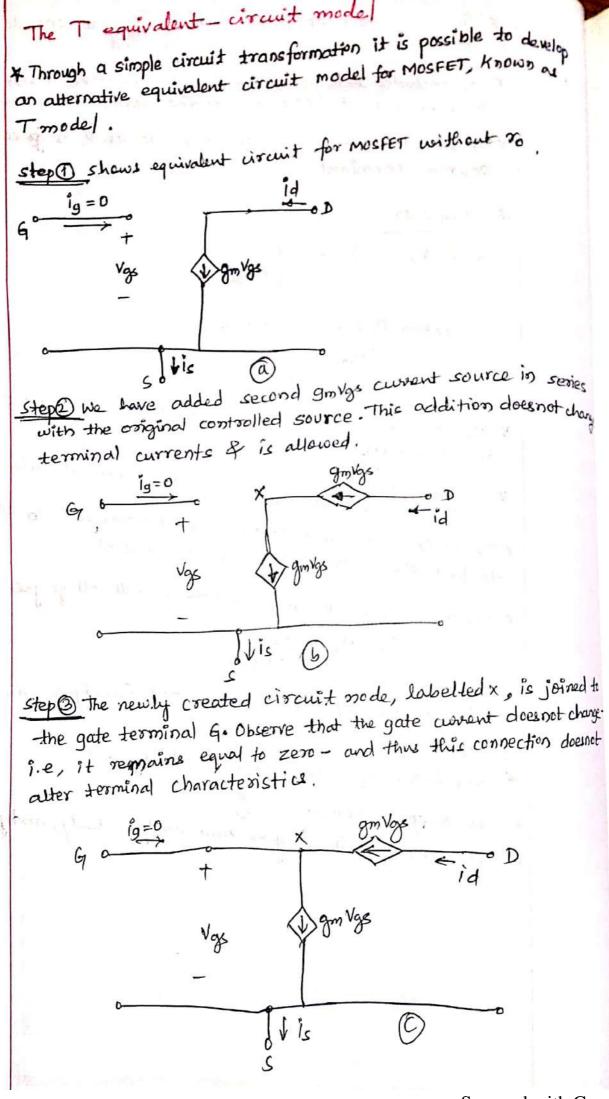

Step 4 : \*\*\* Controlled current cource gmvgs connected across its. Control voltage Vgs. We can replace controlled source by resistance as long as this resistance draws an equal current as the source. Thus, the value of resistance is Vgs/gmvgs = 1/gm. Thus, the value of resistance is Vgs/gmvgs = 1/gm. \*\* which depicts atternative model. Observe that ig is still zero, \*\* which depicts atternative model. Observe that ig is still zero, \*\* which depicts atternative model. Observe that ig is still zero, \*\* which depicts atternative model. Observe that ig is still zero,